Paper 72 Date: April 9, 2020

# UNITED STATES PATENT AND TRADEMARK OFFICE BEFORE THE PATENT TRIAL AND APPEAL BOARD MICROSOFT CORPORATION, Petitioner, v. FG SRC LLC, Patent Owner. IPR2018-01601<sup>2</sup> Patent 7,225,324 B2

Before KALYAN K. DESHPANDE, JUSTIN T. ARBES, and CHRISTA P. ZADO, *Administrative Patent Judges*.

ARBES, Administrative Patent Judge.

JUDGMENT

Final Written Decision

Determining All Challenged Claims Unpatentable

35 U.S.C. § 318(a)

\_

<sup>&</sup>lt;sup>1</sup> Patent Owner filed updated mandatory notice information indicating that DirectStream, LLC ("DirectStream") assigned the challenged patent to FG SRC LLC. Paper 69, 1. Accordingly, the caption for this proceeding has been changed.

<sup>&</sup>lt;sup>2</sup> Cases IPR2018-01602 and IPR2018-01603 have been consolidated with this proceeding.

# I. INTRODUCTION

# A. Background and Summary

Petitioner Microsoft Corporation filed three Petitions, collectively requesting *inter partes* review of claims 1–5, 7–9, 15, 17, 18, and 20–24 of U.S. Patent No. 7,225,324 B2 (Ex. 1001, "the '324 patent") pursuant to 35 U.S.C. § 311(a), as listed in the following chart.<sup>3</sup>

| Case Number   | Challenged Claims    | Petition               |

|---------------|----------------------|------------------------|

| IPR2018-01601 | 1, 8, 9, and 20      | Paper 1 ("Pet.")       |

| IPR2018-01602 | 1, 7, 15, 17, and 24 | Paper 1 ("-1602 Pet.") |

| IPR2018-01603 | 1–5, 18, and 21–23   | Paper 1 ("-1603 Pet.") |

On April 12, 2019, we instituted an *inter partes* review as to all challenged claims on all grounds of unpatentability asserted in the Petitions, and exercised our authority under 35 U.S.C. § 315(d) to consolidate the three proceedings and conduct the proceedings as one trial. Paper 21 ("Decision on Institution" or "Dec. on Inst."). Patent Owner FG SRC LLC subsequently filed a Patent Owner Response (Paper 36, "PO Resp."), Petitioner filed a Reply (Paper 49, "Reply"), and Patent Owner filed a Sur-Reply (Paper 59, "Sur-Reply"). Petitioner filed a Motion to Exclude (Paper 60, "Pet. Mot.") certain evidence submitted by Patent Owner, to which Patent Owner filed an Opposition (Paper 63, "PO Opp.") and Petitioner filed a Reply (Paper 66, "Pet. Mot. Reply"). Patent Owner filed a Motion to Exclude (Paper 61, "PO Mot.") certain evidence submitted by Petitioner, to which Petitioner filed an Opposition (Paper 62, "Pet. Opp.")

<sup>&</sup>lt;sup>3</sup> Unless otherwise noted, references herein are to the exhibits filed in Case IPR2018-01601.

and Patent Owner filed a Reply (Paper 65, "PO Mot. Reply"). An oral hearing was held on February 4, 2020, and a transcript of the hearing is included in the record (Paper 71, "Tr.").

We have jurisdiction under 35 U.S.C. § 6. This Final Written Decision is issued pursuant to 35 U.S.C. § 318(a). For the reasons that follow, we determine that Petitioner has shown by a preponderance of the evidence that claims 1–5, 7–9, 15, 17, 18, and 20–24 are unpatentable.

### B. Related Matters

The parties indicate that the '324 patent is the subject of the following district court cases: *SRC Labs, LLC v. Microsoft Corp.*, No. 2:18-cv-00321 (W.D. Wash.), and *SRC Labs, LLC v. Amazon Web Servs., Inc.*, No. 2:18-cv-00317 (W.D. Wash.). *See* Pet. 3–4; Paper 69, 1.

### C. The '324 Patent

The '324 patent<sup>4</sup> discloses "multi-adaptive processing systems and techniques for enhancing parallelism and performance of computational functions." Ex. 1001, col. 1, ll. 38–41. Parallel processing "allows multiple processors to work simultaneously on the same problem to achieve a solution" in less time than it would take a single processor. *Id.* at col. 1, ll. 42–47. "[A]s more and more performance is required, so is more parallelism, resulting in ever larger systems" and associated difficulties, including "facility requirements, power, heat generation and reliability." *Id.* at col. 1, ll. 51–59. The '324 patent discloses that

<sup>&</sup>lt;sup>4</sup> U.S. Patent No. 7,620,800 B2 (Ex. 1005), a continuation of the '324 patent, is challenged by Petitioner in Case IPR2018-01605. We enter a Final Written Decision in Case IPR2018-01605 concurrently with this Decision.

if a processor technology could be employed that offers orders of magnitude more parallelism per processor, these systems could be reduced in size by a comparable factor. Such a processor or processing element is possible through the use of a reconfigurable processor. Reconfigurable processors instantiate only the functional units needed to solve a particular application, and as a result, have available space to instantiate as many functional units as may be required to solve the problem up to the total capacity of the integrated circuit chips they employ.

Id. at col. 1, l. 63–col. 2, l. 5. The '324 patent describes a known issue where each processor in a multi-processor system is allocated a portion of a problem called a "cell" and "to solve the total problem, results of one processor are often required by many adjacent cells because their cells interact at the boundary." Id. at col. 2, ll. 25–31. Passing intermediate results around the system to complete the problem requires using "numerous other chips and busses that run at much slower speeds than the microprocessor," diminishing performance. Id. at col. 2, ll. 31–37, col. 5, ll. 18–30, Fig. 1 (depicting a conventional multi-processor arrangement). In an adaptive processor-based system, however, "any boundary data that is shared between . . . functional units need never leave a single integrated circuit chip," reducing "data moving around the system" and improving performance. Id. at col. 2, ll. 38–48.

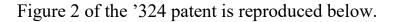

Figure 2 is "a functional block diagram of an adaptive processor 200 communications path for implementing the technique of the present invention." *Id.* at col. 5, ll. 32–35. Adaptive processor 200 includes adaptive processor chip 202, which is coupled to memory element 206, interconnect 208, and additional adaptive processor chips 210. *Id.* at col. 5, ll. 35–40. Adaptive processor chip 202 includes thousands of functional units ("FU") 204 interconnected by "reconfigurable routing resources" inside adaptive processor chip 202, allowing functional units 204 to "exchange data at much higher data rates and lower latencies than a standard microprocessor." *Id.* at col. 5, ll. 41–47.

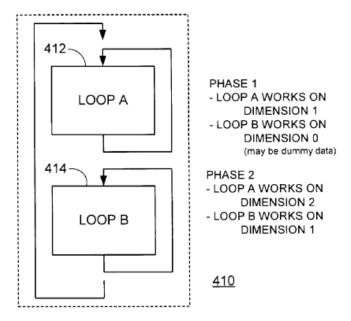

Figures 4A and 4B of the '324 patent are reproduced below.

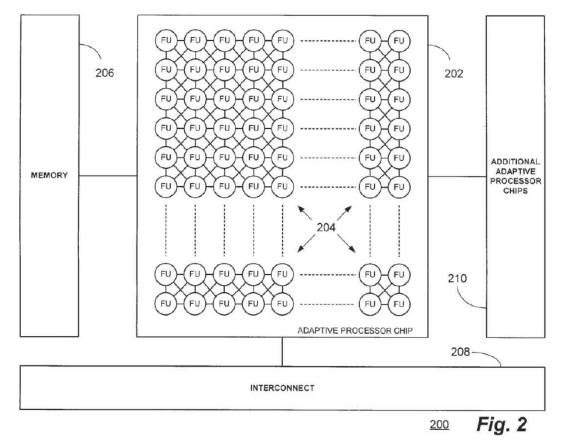

Figure 4A depicts conventional sequential processing operation 400 where "nested Loops A (first loop 402) and B (second loop 404) are alternately active on different phases of the process." *Id.* at col. 6, ll. 1–5. Because first loop 402 must be completed before beginning second loop 404, "all of the logic that has been instantiated is not being completely utilized." *Id.* at col. 6, ll. 6–12. Figure 4B depicts "multi-dimensional process 410 in accordance with the technique of the present invention." Id. at col. 6, 11. 13–16. "[M]ulti-dimensional process 410 is effectuated such that multiple dimensions of data are processed by both Loops A (first loop 412) and B (second loop 414) such that the computing system logic is operative on every clock cycle." *Id.* at col. 6, ll. 16–20. A "dimension" of data can be "multiple vectors of a problem, multiple plans of a problem, multiple time steps in a problem and so forth." *Id.* at col. 6, 11. 27–30. The '324 patent discloses that available resources are utilized more effectively in the multi-dimensional process by "hav[ing] an application evaluate a problem in a data flow sense. That is, it will 'pass' a subsequent dimension of a given

problem through the first loop 412 of logic concurrently with the previous dimension of data being processed through the second loop." *Id.* at col. 6, 11. 21–27.

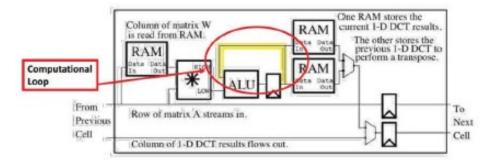

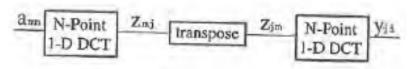

The '324 patent states that the disclosed process can be utilized for a variety of applications. *Id.* at col. 9, 11. 18–29. For example, seismic imaging applications, which "process echo data to produce detailed analysis of subsurface features" for oil and gas exploration, would "particularly benefit from the tight parallelism that can be found in the use of adaptive or reconfigurable processors" because they "use data collected at numerous points and consisting of many repeated parameters" and "the results of the computation on one data point are used in the computation of the next." Id. at col. 9, 11. 35–44; see id. at col. 6, 1. 31–col. 7, 1. 41, Figs. 5A–5B, 6A–6B (describing a seismic imaging function that can be adapted to utilize the disclosed parallelism, where computational process 610 "loops over the depth slices as indicated by reference number 622 and loops over the shots as indicated by reference number 624"). Also, reservoir simulation applications, which "process fluid flow data in . . . oil and gas subsurface reservoirs to produce extraction models," would benefit from the disclosed process because they define a three dimensional set of cells for the reservoir, utilize repeated operations on each cell, and "information computed for each cell is then passed to neighboring cells." *Id.* at col. 10, ll. 2–13; see id. at col. 7, 1. 42-col. 8, 1. 26, Figs. 7A-7D (describing "process 700 for performing a representative systolic wavefront operation in the form of a reservoir simulation function" in which "the computation of fluid flow properties are communicated to neighboring cells 710" without storing data in memory, "a set of cells can reside in an adaptive processor," and "the pipeline of computation can extend across multiple adaptive processors,"

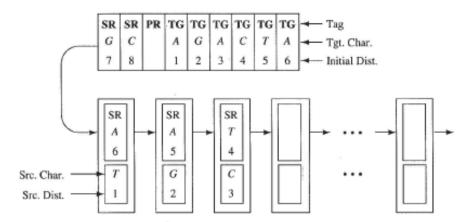

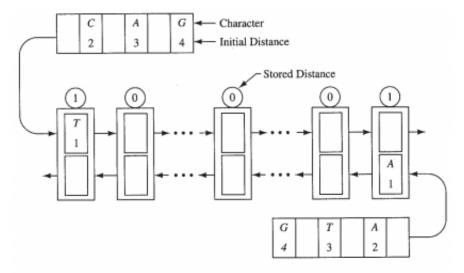

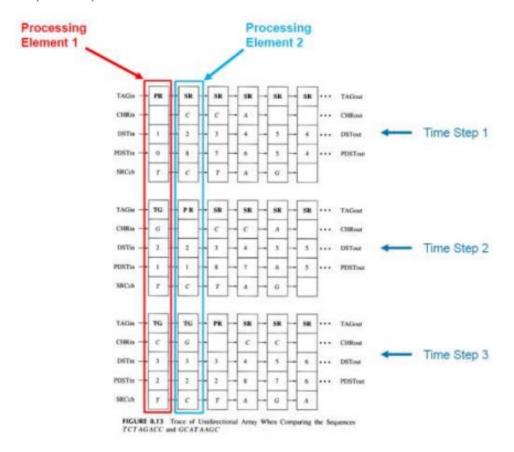

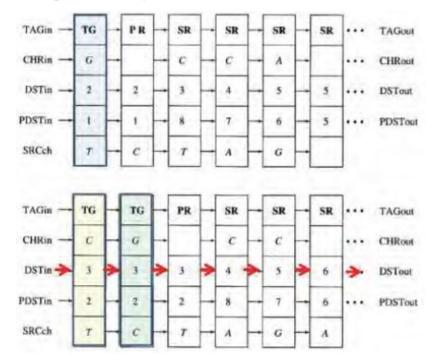

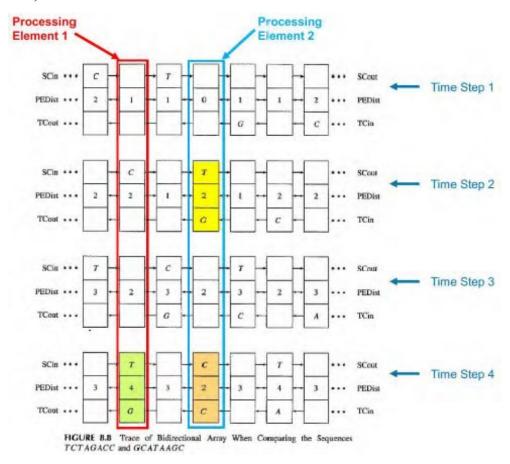

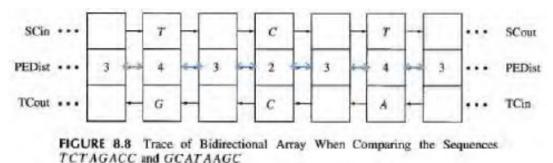

where the process involves nested loops and systolic walls 712 and 714 of computation at different time sets), col. 8, l. 27–col. 9, l. 17, Figs. 8A–8C, 9A–9C (describing two other processes for performing "a representative systolic wavefront operation"). Finally, the disclosed process may be used for genetic pattern matching applications, which "look[] for matches of a particular genetic sequence (or model) to a database of genetic records," performing repeated operations to "compare[] each character in the model to the characters in [a particular] genetic record." *Id.* at col. 11, ll. 55–64.

# D. Illustrative Claims

Claim 1 of the '324 patent is independent. Claims 2–5, 7–9, 15, 17, 18, and 20–24 each depend from claim 1. Claims 1 and 15 recite:

1. A method for data processing in a reconfigurable computing system, the reconfigurable computing system comprising at least one reconfigurable processor, the reconfigurable processor comprising a plurality of functional units, said method comprising:

transforming an algorithm into a calculation that is systolically implemented by said reconfigurable computing system at the at least one reconfigurable processor;

instantiating at least two of said functional units at the at least one reconfigurable processor to perform said calculation wherein only functional units needed to solve the calculation are instantiated and wherein each instantiated functional unit at the at least one reconfigurable processor interconnects with each other instantiated functional unit at the at least one reconfigurable processor based on reconfigurable routing resources within the at least one reconfigurable processor as established at instantiation, and wherein systolically linked lines of code of said calculation are instantiated as clusters of functional units within the at least one reconfigurable processor;

utilizing a first of said instantiated functional units to operate upon a subsequent data dimension of said calculation forming a first computational loop; and

substantially concurrently utilizing a second of said instantiated functional units to operate upon a previous data dimension of said calculation forming a second computational loop wherein said systolic implementation of said calculation enables said first computational loop and said second computational loop execute concurrently and pass computed data seamlessly between said computational loops.

15. The method of claim 1 wherein instantiating includes establishing a stream communication connection between functional units.

# E. Evidence

The pending grounds of unpatentability in the instant *inter partes* review are based on the following prior art:

Jean-Luc Gaudiot, "Data-Driven Multicomputers in Digital Signal Processing," *Proceedings of the IEEE, Special Issue on Hardware and Software for Digital Signal Processing*, vol. 75, no. 9, Sept. 1987, pp. 1220–1234 (Ex. 1010, "Gaudiot");

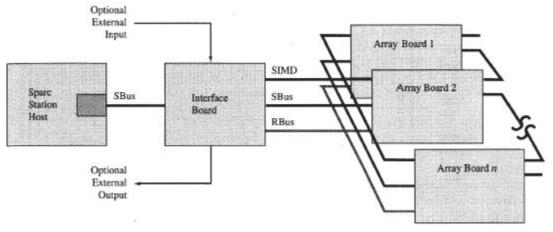

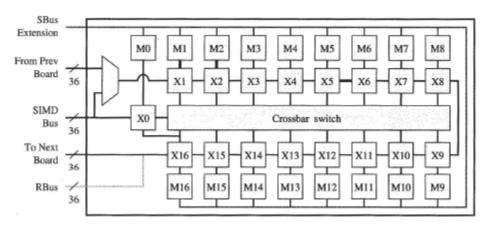

Duncan A. Buell, Jeffrey M. Arnold, & Walter J. Kleinfelder, SPLASH2: FPGAS IN A CUSTOM COMPUTING MACHINE (1996) (Ex. 1007, "Splash2");

Carl Ebeling *et al.*, "Mapping Applications to the RaPiD Configurable Architecture," *Proceedings of the IEEE Symposium on FPGAs for Custom Computing Machines*, Apr. 16–18, 1997, pp. 106–115 (Ex. 1009, "RaPiD");

Michael Rencher & Brad L. Hutchings, "Automated Target Recognition on SPLASH 2," *Proceedings of the IEEE Symposium on FPGAs for Custom Computing Machines*, Apr. 16–18, 1997, pp. 192–200 (Ex. 1011, "Chunky SLD");

Yong-Jin Jeong & Wayne P. Burleson, "VLSI Array Algorithms and Architectures for RSA Modular Multiplication," *IEEE*

Transactions on Very Large Scale Integration (VLSI) Systems, vol. 5, no. 2, June 1997, pp. 211–217 (Ex. 1061, "Jeong"); and

D. Roccatano *et al.*, "Development of a Parallel Molecular Dynamics Code on SIMD Computers: Algorithm for Use of Pair List Criterion," *Journal of Computational Chemistry*, vol. 19, no. 7, May 1998, pp. 685–694 (Ex. 1012, "Roccatano").<sup>5</sup>

Petitioner filed a declaration from Harold Stone, Ph.D. (Ex. 1003) with its Petition and a reply declaration from Dr. Stone (Ex. 1076) with its Reply. Patent Owner filed declarations from Jon Huppenthal (Ex. 2100), Houman Homayoun, Ph.D. (Exs. 2029, 2111), and Tarek El-Ghazawi, Ph.D. (Ex. 2164).

# F. Asserted Grounds

The instant *inter partes* review involves the following grounds of unpatentability:

| Petition(s)                                       | Claim(s)<br>Challenged | 35 U.S.C. §                    | Reference(s)/Basis |

|---------------------------------------------------|------------------------|--------------------------------|--------------------|

| IPR2018-01601,<br>IPR2018-01602,<br>IPR2018-01603 | 1, 15, 18, 21,<br>22   | 102(a),<br>102(b) <sup>6</sup> | Splash2            |

| IPR2018-01601,<br>IPR2018-01602,<br>IPR2018-01603 | 1, 15, 18, 21,<br>22   | 103(a)                         | Splash2            |

\_

<sup>&</sup>lt;sup>5</sup> When citing the prior art references and other exhibits, we refer to the page numbers in the bottom-right corner added by the filing party. *See* 37 C.F.R. § 42.63(d)(2).

<sup>&</sup>lt;sup>6</sup> The Leahy-Smith America Invents Act, Pub. L. No. 112-29, 125 Stat. 284 (2011) ("AIA"), amended 35 U.S.C. §§ 102 and 103. Because the challenged claims of the '324 patent have an effective filing date before the effective date of the applicable AIA amendments, we refer to the pre-AIA versions of 35 U.S.C. §§ 102 and 103.

| Petition(s)                                       | Claim(s)<br>Challenged | 35 U.S.C. § | Reference(s)/Basis              |

|---------------------------------------------------|------------------------|-------------|---------------------------------|

| IPR2018-01601,<br>IPR2018-01602,<br>IPR2018-01603 | 1, 15, 18, 21,<br>22   | 103(a)      | Splash2, Gaudiot                |

| IPR2018-01601                                     | 8, 9                   | 103(a)      | Splash2, RaPiD                  |

| IPR2018-01601                                     | 8, 9                   | 103(a)      | Splash2, RaPiD,<br>Gaudiot      |

| IPR2018-01601                                     | 20                     | 103(a)      | Splash2, Jeong                  |

| IPR2018-01601                                     | 20                     | 103(a)      | Splash2, Jeong,<br>Gaudiot      |

| IPR2018-01602                                     | 7, 17, 24              | 103(a)      | Splash2, Chunky<br>SLD          |

| IPR2018-01602                                     | 7, 17, 24              | 103(a)      | Splash2, Chunky<br>SLD, Gaudiot |

| IPR2018-01603                                     | 2–5, 22, 23            | 103(a)      | Splash2, Roccatano              |

| IPR2018-01603                                     | 2–5, 22, 23            | 103(a)      | Splash2, Roccatano,<br>Gaudiot  |

# II. ANALYSIS

# A. Motions to Exclude

The party moving to exclude evidence bears the burden of proof to establish that it is entitled to the relief requested—namely, that the material sought to be excluded is inadmissible under the Federal Rules of Evidence. *See* 37 C.F.R. §§ 42.20(c), 42.62(a). For the reasons discussed below, Petitioner's Motion is granted-in-part, denied-in-part, and dismissed-in-part, and Patent Owner's Motion is denied-in-part and dismissed-in-part.

## 1. Petitioner's Motion to Exclude

Exhibits 2100, 2066, 2076, and 2092: Petitioner moves to exclude the entirety of the declaration (Ex. 2100) of Mr. Huppenthal, one of the named inventors of the '324 patent, "as not being relevant to any issue on which trial has been instituted, and for lacking foundation, containing hearsay, and/or causing undue prejudice." Pet. Mot. 3–6. Petitioner argues that the declaration includes "irrelevant narrative discussion of [Mr. Huppenthal's] participation in reconfigurable computing" and statements "either based on hearsay or lack of personal knowledge." *Id.* at 3–4. Petitioner also moves to exclude paragraphs 80 and 82–86 of the declaration based on Mr. Huppenthal's alleged "refusal to answer questions concerning those portions of the declaration" during cross-examination. *Id.* at 1–3.

Petitioner also moves to exclude three transcripts (Exs. 2066, 2076, 2092) of depositions of Petitioner's declarants from other *inter partes* reviews as "not being relevant to any issue on which trial has been instituted, for containing hearsay, and/or causing undue prejudice." *Id.* at 6–7. Petitioner argues that allowing the transcripts in the record would be "highly prejudicial as they present themselves with the indicia of expert testimony while being totally devoid from the necessary context of the matters from which they originate." *Id.* Patent Owner cites Exhibits 2066 and 2076 in its Response, but does not cite Exhibit 2092 in its Response or Sur-Reply.

Petitioner's Motion is dismissed as moot, as we do not rely on the cited portions of the testimony in a manner adverse to Petitioner in this Decision. As explained below, even if the testimony is considered, we are not persuaded by Patent Owner's arguments regarding the state of the art or alleged nonobviousness of the challenged claims, and Patent Owner has not

shown proof of secondary considerations that would support a conclusion of nonobviousness. *See infra* Sections II.E–II.J.

Exhibit 2111: Petitioner moves to exclude paragraphs 41, 145, 180, 181, and 247 of the declaration of Dr. Homayoun, which refer to Exhibits 2066 and 2100. Pet. Mot. 8–9. Because we do not exclude those exhibits, we also dismiss as moot Petitioner's Motion with respect to Exhibit 2111.

Exhibits 2067–2075, 2077, 2079–2099, 2101–2103, 2105, 2106, 2109, 2110, 2112–2133, 2139–2151, 2155, 2161–2163, and 2168:

Petitioner moves to exclude a number of exhibits as "not being relevant to any issues on which trial has been instituted, lacking foundation, and/or causing undue prejudice" because the exhibits were not discussed or cited, or "only cited superficially," in Patent Owner's Response and Sur-Reply.

Pet. Mot. 7–8. Petitioner's Motion is dismissed as moot, as we do not rely on the exhibits in a manner adverse to Petitioner in this Decision. We note, however, that in evaluating Petitioner's asserted grounds of unpatentability, we only consider substantive arguments made by the parties in their papers during trial (i.e., the Petitions, Response, Reply, and Sur-Reply). To the extent a document is filed in the record but never discussed in a paper, there is no substantive argument pertaining to that document that can be considered.

Exhibit 2168: Petitioner moves to exclude Exhibit 2168 under Federal Rules of Evidence 401–403 as cumulative of Exhibit 1007. Pet. Mot. 8. Both exhibits are copies of Splash2. Dr. El-Ghazawi refers to the document in his declaration with the numeral "1007." Ex. 2164 ¶ 40. To ensure a clear record, we grant Petitioner's Motion, expunge Exhibit 2168, and refer herein to Exhibit 1007. See 37 C.F.R. §§ 42.7(a), 42.6(d) ("A document already in the record of the proceeding must not be filed

again, not even as an exhibit or an appendix, without express Board authorization.").

Portions of Patent Owner's Response: Petitioner moves to exclude portions of Patent Owner's Response referring to the exhibits that Petitioner seeks to exclude. Pet. Mot. 9. Patent Owner's Response is a paper with attorney arguments, not evidence that may be excluded. Further, we do not exclude any of the exhibits referred to in the identified portions of the Response. Petitioner's Motion is denied as to Patent Owner's Response.

### 2. Patent Owner's Motion to Exclude

Exhibits 1074, 1077, and 1079: Patent Owner moves to exclude three technical documents filed by Petitioner with its Reply.

First, Patent Owner moves to exclude Exhibits 1074 and 1079 as unauthenticated under Federal Rule of Evidence 901. PO Mot. 6–7. "To satisfy the requirement of authenticating or identifying an item of evidence, the proponent must produce evidence sufficient to support a finding that the item is what the proponent claims it is." Fed. R. Evid. 901(a). Certain evidence, though, is "self-authenticating" and "require[s] no extrinsic evidence of authenticity in order to be admitted." Fed. R. Evid. 902. Exhibit 1074 is an article by Maya Gokhale and Ron Minnich titled "FPGA Computing in a Data Parallel C," and includes an IEEE trade inscription, copyright symbol, and International Standard Book Number (ISBN) on the first page ("0-8186-3890-7/93 \$03.00 © 1993 IEEE"). It is

<sup>&</sup>lt;sup>7</sup> Petitioner did not seek authorization to file a motion to strike Patent Owner's Response. *See* Patent Trial and Appeal Board Consolidated Trial Practice Guide (Nov. 2019), 80–81, *available at* https://www.uspto.gov/TrialPracticeGuideConsolidated ("Trial Practice Guide").

self-authenticating under at least Federal Rule of Evidence 902(6) ("Printed material purporting to be a . . . periodical.") and 902(7) ("An inscription, sign, tag, or label purporting to have been affixed in the course of business and indicating origin, ownership, or control."). Exhibit 1079 is an excerpt from a book by Kevin Skahill titled "VHDL for Programmable Logic." It includes a copyright notice ("Copyright © 1996 by Addison-Wesley Publishing, Inc."), Library of Congress catalogue information, and hand-written library catalogue information. Ex. 1079, Cover 3, v. Petitioner points out where the book is available from "several well-known book sellers." Pet. Opp. 4 & n.2. It is authenticated at least as an ancient document under Federal Rule of Evidence 901(b)(8) because it "is in a condition that creates no suspicion about its authenticity," "was in a place where, if authentic, it would likely be," and "is at least 20 years old when offered." Nothing about either exhibit suggests that it is not what it points to be, and Patent Owner does not point to anything in particular in the exhibits that would indicate otherwise. See PO Mot. 6–7; PO Mot. Reply 1–4.

Second, Patent Owner moves to exclude Exhibits 1074, 1077, and 1079 as containing inadmissible hearsay under Federal Rule of Evidence 802. PO Mot. 7. Patent Owner states that Petitioner in its Reply "cites each of these documents to prove the truth of technical matters allegedly asserted in such documents, *i.e.* to support Petitioner's specific factual assertions regarding a technical issue." *Id.* We are not persuaded. Patent Owner does not identify any particular "statement" in any of the exhibits that is being offered "to prove the truth of the matter asserted in the statement," and thus fails to meet its burden to prove inadmissibility as hearsay. *See* Fed. R. Evid. 801(c); 37 C.F.R. § 42.20(c). Even if Patent Owner had done so, Petitioner cites the exhibits to show what a person of ordinary skill in the art

would have known at the time of the '324 patent and, with respect to Exhibit 1074 in particular, how a person of ordinary skill in the art would have understood another reference relied on by Patent Owner that cites the article. *See* Reply 7, 17, 33; Pet. Opp. 5–6; Ex. 2167, 37–38, 208. The exhibits are not being offered for the truth of any particular matter discussed in the references. Finally, Exhibits 1074 and 1079 also are admissible under Federal Rule of Evidence 803(16), which provides as an exception to the hearsay rule "[a] statement in a document that was prepared before January 1, 1998, and whose authenticity is established." *See* 1074, 94 ("1993" date); Ex. 1079, Cover 3, v ("1996" date).

Third, Patent Owner moves to exclude Exhibit 1077 as "irrelevant to the patent and claim construction issues in dispute." PO Mot. 7–8. Exhibit 1077 is an excerpt of certain pages of the Microsoft Computer Dictionary (5th ed. 2002). Patent Owner argues that Exhibit 1077 "is extrinsic evidence pertaining to Petitioner's proffered definitions from the Microsoft Computer Dictionary of 'data structure' and 'data path,' neither of which are claim terms in the patent." PO Mot. 7. Federal Rule of Evidence 401 provides that "[e]vidence is relevant if: (a) it has any tendency to make a fact more or less probable than it would be without the evidence; and (b) the fact is of consequence in determining the action."

Petitioner submits Exhibit 1077 in support of its arguments regarding the interpretation of disputed claim language, specifically the term "stream communication." Reply 33. The meaning of this phrase is "of consequence in determining" whether challenged claim 15 is unpatentable over the asserted prior art, and Exhibit 1077 provides insight as to the meaning of words used in both parties' proposed interpretations. *See infra* Section II.C.4. Exhibit 1077 has some "tendency to make a fact more or less

probable than it would be without the evidence" and is relevant under Federal Rule of Evidence 401. Thus, there is no basis to exclude Exhibit 1077. We also note that Patent Owner appears to have filed a full copy of the dictionary as Exhibit 2065, and the same pages filed as Exhibit 1077 (pages 144–145) that Patent Owner seeks to exclude are in the exhibit that Patent Owner filed. Further, the record contains numerous other dictionary references filed by both parties, including Exhibits 1025, 1059, 2024–2026, and 2038. Patent Owner's Motion is denied as to Exhibits 1074, 1077, and 1079.

Exhibit 1076: Patent Owner also moves to exclude paragraphs 15–17 of the reply declaration of Dr. Stone, which refer to Exhibit 1074 "for the first time," under Federal Rules of Evidence 402 and 403. PO Mot. 8. Because we find no basis to exclude Exhibit 1074, we also deny Patent Owner's Motion with respect to Exhibit 1076. To the extent Patent Owner's position is that Petitioner's Reply and Dr. Stone's reply declaration exceed the proper scope of a reply, we address those arguments below. See infra Section II.E.2.a.2; Trial Practice Guide, 79 ("A motion to exclude is not a vehicle for addressing the weight to be given evidence—arguments regarding weight should appear only in the merits documents. Nor should a motion to exclude address arguments or evidence that a party believes exceeds the proper scope of reply or sur-reply.").

Exhibits 1075 and 1078: Patent Owner moves to exclude certain portions of the transcript of the deposition of Dr. Homayoun because the questions asked were "vague, ambiguous, call[] for a legal conclusion, and misleading." PO Mot. 9–11 (citing Ex. 1075, 27:4–12, 65:5–17). Patent Owner also moves to exclude a portion of the transcript of the deposition of Dr. El-Ghazawi because the question asked was "vague, ambiguous, and

calls for a speculative answer." *Id.* at 11 (citing Ex. 1078, 65:12–17). Patent Owner's Motion is dismissed as moot, as we do not rely on the disputed portions of the testimony in rendering our Decision.

# B. Level of Ordinary Skill in the Art

In determining the level of ordinary skill in the art for a challenged patent, we look to "1) the types of problems encountered in the art; 2) the prior art solutions to those problems; 3) the rapidity with which innovations are made; 4) the sophistication of the technology; and 5) the educational level of active workers in the field." *Ruiz v. A.B. Chance Co.*, 234 F.3d 654, 666–667 (Fed. Cir. 2000). "Not all such factors may be present in every case, and one or more of them may predominate." *Id*.

Petitioner's declarant, Dr. Stone, testifies that a person of ordinary skill in the art at the time of the '324 patent would have had "an advanced degree in electrical or computer engineering, or computer science with substantial study in computer architecture, hardware design, and computer algorithms," and "at least three years' experience working in the field," or alternatively "a bachelor's degree covering those disciplines and at least four years working [in] the field." Ex. 1003 ¶ 45. According to Dr. Stone,

[s]uch a person would also have been knowledgeable about the programming, design and operation of computer systems based on reconfigurable components such as FPGAs (field programmable gate arrays) and CPLDs (complex programmable logic devices), including computer systems for performing systolic and data driven calculations. That person would also have been familiar with hardware description languages such as [Very High Speed Integrated Circuit Hardware Description Language (VHDL)] that could be used to configure FPGAs and CPLDS that serve as components of reconfigurable computer systems. Finally, as demonstrated by many of the references

discussed [in Dr. Stone's declaration], such a person would also have been familiar with various other areas of technology that by 2002 had relied on high performance and parallel computing systems, such as genetic sequence comparisons, image processing, data mining, and processing related to proteins and organic structures.

Id.

Patent Owner states that it "does not dispute the level of education and skill promoted by [Dr. Stone]," and Patent Owner's declarant, Dr. Homayoun, "agree[d] with Dr. Stone's assessment of the level of ordinary skill in the art," noting that such an individual also would have been "experienced in developing with high-level languages (C and Fortran), hardware description languages, and the unique problems involved with programming FPGAs and FPGA based systems." See PO Resp. 29; Ex. 2029 ¶ 17; see also Ex. 2111 ¶ 133 ("In general, I would agree to the level of education and skill promoted by [Petitioner's] expert [for the '324 patent]."). Dr. Homayoun further expands on his understanding of what a person of ordinary skill in the art at the time of the '324 patent would have known and considered. Ex. 2111 ¶¶ 133–146. For example, Dr. Homayoun testifies that in addition to the technical background set forth in Dr. Stone's definition, a person of ordinary skill in the art would have "considered all of the state of the art [described in Dr. Homayoun's declaration] in the design of computer architecture, . . . [i]ncluding the issues of reconfigurable programming, processor speed, FPGA speed, and cost/benefit analysis of overhead introduction as applied to [high performance computing (HPC)] applications." Id. ¶ 133. Also, according to Dr. Homayoun, an ordinarily skilled artisan would have "consider[ed] the technical problems [the '324 patent was] attempting to solve" without using

the patent "as a technical road-map to then conflate the technical problem with the solution," and "would have considered the drawbacks in HPC computing and the deficiencies in FPGA systems and computer architecture design considerations at the time of the disclosed inventions." *Id.* ¶ 140. Patent Owner similarly argues in its Response that a person of ordinary skill in the art would have "considered" all of these issues. PO Resp. 17–29.

We have evaluated all of Patent Owner's arguments and supporting evidence regarding what a person of ordinary skill in the art allegedly would have considered when reading the asserted references. Patent Owner's arguments pertain more to its criticism of Dr. Stone's analysis as allegedly failing to understand the problems solved by the '324 patent and being based on "hindsight bias" than a dispute over the "level" of ordinary skill in the art. See id. (also arguing that "Petitioner essentially uses the patent itself as a roadmap for stitching together various prior art references"); Sur-Reply 1–8; Tr. 64:4–65:15. It suffices at this point to conclude that a person of ordinary skill in the art would have had the technical education and work experience set forth in Dr. Stone's declaration (and agreed to by Dr. Homayoun). See Tr. 64:13–14 (Patent Owner stating that there is no dispute as to "the level of education"). Among other things, such an individual would have had knowledge of "multi-adaptive processing systems and techniques," "parallel processing," and field-programmable gate arrays (FPGAs). See Ex. 1001, col. 1, 11. 35–59; Ex. 1003 ¶ 45; Ex. 2029 ¶ 17; Ex. 2111 ¶¶ 107–119, 133; Ex. 1007, 1–9; Custom Accessories, Inc. v. Jeffrey-Allan Indus., Inc., 807 F.2d 955, 962 (Fed. Cir. 1986) ("The person of ordinary skill is a hypothetical person who is presumed to be aware of all the pertinent prior art."). What that individual would have considered in evaluating particular

prior art references and making potential combinations, though, is an issue we address below in evaluating Petitioner's grounds of unpatentability.<sup>8</sup>

Based on the full record developed during trial, including our review of the '324 patent and the types of problems and prior art solutions described in the '324 patent, as well as the sophistication of the technology described in the '324 patent, we conclude that a person of ordinary skill in the art would have had (1) an advanced degree in electrical or computer engineering, or computer science with substantial study in computer architecture, hardware design, and computer algorithms, and at least three years of experience working in the field, or (2) a bachelor's degree covering those disciplines and at least four years working in the field. We apply that level of skill for purposes of this Decision.

# C. Claim Interpretation

In this proceeding, we interpret the claims of the unexpired '324 patent using the "broadest reasonable construction in light of the

<sup>&</sup>lt;sup>8</sup> We note that for Petitioner's anticipation ground based on Splash2, the level of ordinary skill in the art is relevant to understanding how a person of ordinary skill in the art would have interpreted the claims and understood the reference, but not with respect to, for example, any motivations or problems a person of ordinary skill in the art would have had in combining teachings. *See Wasica Finance GmbH v. Continental Auto. Sys., Inc.*, 853 F.3d 1272, 1284 (Fed. Cir. 2017) ("Anticipation is an inquiry viewed from the perspective of one skilled in the art."); *Vivint, Inc. v. Alarm.com Inc.*, 741 F. App'x 786, 791–792 (Fed. Cir. 2018) (unpublished) ("While anticipation is proven based on the express and inherent teachings of a single prior art reference, an obviousness analysis reaches beyond the prior art reference and takes into account other considerations such as the level of ordinary skill in the art and any objective indicia of nonobviousness.").

specification of the patent." 37 C.F.R. § 42.100(b) (2017). Under this standard, we interpret claim terms using "the broadest reasonable meaning of the words in their ordinary usage as they would be understood by one of ordinary skill in the art, taking into account whatever enlightenment by way of definitions or otherwise that may be afforded by the written description contained in the applicant's specification." In re Morris, 127 F.3d 1048, 1054 (Fed. Cir. 1997); see In re Smith Int'l, Inc., 871 F.3d 1375, 1382-83 (Fed. Cir. 2017) ("[The] broadest reasonable interpretation . . . is an interpretation that corresponds with what and how the inventor describes his invention in the specification."). "Under a broadest reasonable interpretation, words of the claim must be given their plain meaning, unless such meaning is inconsistent with the specification and prosecution history." TriVascular, Inc. v. Samuels, 812 F.3d 1056, 1062 (Fed. Cir. 2016). Our interpretation "cannot be divorced from the specification and the record evidence,' and 'must be consistent with the one that those skilled in the art would reach.' A construction that is 'unreasonably broad' and which does not 'reasonably reflect the plain language and disclosure' will not pass muster." Microsoft Corp. v. Proxyconn, Inc., 789 F.3d 1292, 1298 (Fed. Cir.

\_

<sup>&</sup>lt;sup>9</sup> The Petitions in this proceeding were filed on September 5, 2018, prior to the effective date of the rule change that replaces the broadest reasonable interpretation standard with the federal court claim interpretation standard. *See* Changes to the Claim Construction Standard for Interpreting Claims in Trial Proceedings Before the Patent Trial and Appeal Board, 83 Fed. Reg. 51,340, 51,340, 51,358 (Oct. 11, 2018) (amending 37 C.F.R. § 42.100(b) effective November 13, 2018) (now codified at 37 C.F.R. § 42.100(b) (2019)); *Game & Tech. Co. v. Wargaming Grp. Ltd.*, 942 F.3d 1343, 1351 (Fed. Cir. 2019) ("If, as here, the [*inter partes* review] stems from a petition filed before November 13, 2018, the claims are given the 'broadest reasonable interpretation' consistent with the specification." (citation omitted)).

2015) (citations omitted), *overruled on other grounds by Aqua Prods., Inc.* v. *Matal*, 872 F.3d 1290 (Fed. Cir. 2017).

Upon review of the parties' arguments during trial and the evidence as a whole, we conclude that three terms in claim 1 ("systolic," "computational loop," and "pass computed data seamlessly between said computational loops") and one term in claim 15 ("establishing a stream communication connection between functional units") require interpretation.

# 1. "Systolic"

Claim 1 recites "transforming an algorithm into a calculation that is systolically implemented by said reconfigurable computing system at the at least one reconfigurable processor," wherein "systolically linked lines of code of said calculation are instantiated as clusters of functional units within the at least one reconfigurable processor" and "said systolic implementation of said calculation enables said first computational loop and said second computational loop execute concurrently and pass computed data seamlessly between said computational loops" (emphases added).

In the Decision on Institution, based on the parties' arguments and record at the time, we preliminarily interpreted the term "systolic" recited in claim 1 to mean "the characteristic of rhythmically computing and passing data directly between processing elements in a manner that is transport triggered (i.e., by the arrival of a data object) rather than a program counter or clock driving movement of the data." Dec. on Inst. 17–21. Petitioner agrees with that interpretation. Reply 26. Patent Owner argues that "systolic" has a "plain and ordinary meaning and need not be construed," but if the term is interpreted, it means "[a]n array of many interconnected

functional units that operates in a data flow sense and allows different data to flow in different directions." PO Resp. 42, 50.

Based on our review of the full trial record, we maintain our preliminary conclusion in the Decision on Institution that the applicants described the plain meaning of "systolic" during prosecution of the '324 patent. *See* Dec. on Inst. 17–21. Specifically, following an Office Action rejecting claim 1 under 35 U.S.C. § 112, first paragraph, and 35 U.S.C. § 103, the applicants conducted an interview with the examiner and proposed, among other amendments, adding the "systolic" language above to the claim. Ex. 1002, 186–212. The applicants then filed an Office Action response amending the claim, noting that the examiner had requested during the interview that the applicants "further define the term[s] instantiated and systolic" and arguing the following in response to the 35 U.S.C. § 112, first paragraph, written description rejection:

[T] he term systolic computation is derived from continual and pulsating pumping of the human heart. In computer architecture a systolic array is an arrangement of data processing units similar to a central processing unit but without a program counter or clock that drives the movement of data. That is because the operation of the systolic array is transport triggered, i.e. by the arrival of a data object. Data flows across the array between functional units, usually with different data flowing in different directions. David J. Evans in his work, Systolic algorithms. Systolic algorithms, number 3 in Topics in Computer Mathematics. Gordon and Breach, 1991 define a Systolic system as a "network of processors which *rhythmically* compute an[d] pass data through the system[.]" Thus in the Applicant's invention Systolic implementation will connect computational loops such that data from one compute loop will be passed as input data to a concurrently executing compute In the Applicant's invention data computed by loop. computation units or groups of functional units flows seamlessly and concurrently with data being computed by other groups of functional units. Thus, the process claimed by the Applicant therefore significantly increases the computing processes taking place in a reconfigurable processor.

Ex. 1002, 224–226 (emphases added); see also id. at 119 (stating that the term "systolic," coined by H.T. Kung of Carnegie-Mellon, refers to the rhythmic transfer of data through the pipeline, like blood flowing through the vascular system"). Importantly, after the applicants filed the Office Action response amending claim 1 to include the "systolic" language and making the above argument, the examiner allowed the claims. *Id.* at 234–238. During prosecution, "an applicant's amendment accompanied by explanatory remarks can define a claim term by demonstrating what the applicant meant by the amendment." *Personalized Media Comm'cns, LLC v. Apple Inc.*, 952 F.3d 1336, 1340 (Fed. Cir. 2020). Patent Owner acknowledges that the prosecution history argument quoted above was "an explanation of the plain and ordinary meaning of the term 'systolic." PO Resp. 47.

Our interpretation also is consistent with the Specification, in particular the description of Figures 8A and 8B showing an exemplary "systolic" operation where "data is continually passed directly from one computational loop to another for processing without intervening structures between the loops" and without a program counter or clock driving movement of the data. Ex. 1003 ¶ 70; see Ex. 1001, col. 8, ll. 27–45 (disclosing a "representative systolic wavefront operation" in which "systolic processing in the process 800 can pass previously computed data down within a column" and "to subsequent columns as well," with the computational loops operating concurrently); Ex. 1002, 227 (applicants

IPR2018-01601 Patent 7,225,324 B2

citing Figures 8A and 8B and the accompanying text as a "a systolic wave front operation" during prosecution of the '324 patent).

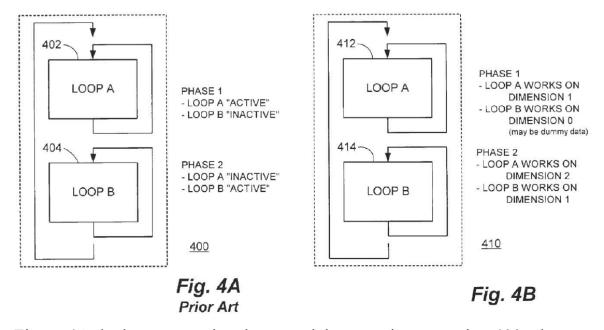

Other documentation from the time also shows that the applicants' description of the term "systolic" is how a person of ordinary skill in the art would have understood the term. H.T. Kung, *Why Systolic Architectures*?, IEEE Jan. 1982 (Ex. 1016, "Kung"), discloses:

A systolic system consists of a set of interconnected cells, each capable of performing some simple operation. Because simple, regular communication and control structures have substantial advantages over complicated ones in design and implementation, cells in a systolic system are typically interconnected to form a systolic array or a systolic tree. Information in a systolic system flows between cells in a pipelined fashion, and communication with the outside world occurs only at the "boundary cells." For example, in a systolic array, only those cells on the array boundaries may be I/O ports for the system.

. . .

The basic principle of a systolic architecture, a systolic array in particular, is illustrated in Figure 1. By replacing a single processing element with an array of [processing elements], or cells in the terminology of this article, a higher computation throughput can be achieved without increasing memory bandwidth. The function of the memory in the diagram is analogous to that of the heart; it "pulses" data (instead of blood) through the array of cells. The crux of this approach is to ensure that once a data item is brought out from the memory it can be used effectively at each cell it passes while being "pumped" from cell to cell along the array. This is possible for a wide class of compute-bound computations where multiple operations are performed on each data item in a repetitive manner.

Id. at 39 (emphases added).

Figure 1 of Kung is reproduced below.

Figure 1. Basic principle of a systolic system.

Figure 1 depicts how data travels and interacts with memory using a systolic array of processing elements versus a single processing element. *Id.* at 38. Another reference by the same author states:

A systolic system is a network of processors which rhythmically compute and pass data through the system. . . . In a systolic computing system, the function of a processor is analogous to that of the heart. Every processor regularly pumps data in and out, each time performing some short computation, so that a regular flow of data is kept up in the network.

Ex. 1015, 5. Including in the interpretation "rhythmically computing and passing data directly between processing elements" and operating in a "transport triggered" manner is consistent with Kung's description of each processing element processing data and "puls[ing]" or "pump[ing]" it to the next processing element in the array. *See* Ex. 1016, 39; Ex. 1003 ¶¶ 76–78.

Patent Owner in its Response relies on the same portions of the prosecution history and Kung discussed above. *See* PO Resp. 42–50. That evidence, however, supports our preliminary interpretation, not Patent Owner's proposed interpretation, for the reasons explained above. Patent Owner also argues that "systolic means an array of interconnected processing elements that only interact with memory at the array boundaries so that the data is processed by multiple processing elements before

returning to memory." PO Resp. 44–48 (citing Ex. 1001, col. 2, ll. 38–42, Fig. 2; Ex. 2046 ¶ 16; Ex. 2111 ¶¶ 125–131, 177). We do not see how that undermines the preliminary interpretation, however. Logically, if processing elements interact with memory *only* at array boundaries, there can be no memory receiving data between the processing elements; data would be passed "directly" between them. *See* Reply 29. We further address the parties' arguments regarding the use of the word "directly" in interpreting "pass computed data seamlessly between said computational loops" below. *See infra* Section II.C.3.

Applying the broadest reasonable interpretation of the claims in light of the Specification, we interpret "systolic" to mean "the characteristic of rhythmically computing and passing data directly between processing elements in a manner that is transport triggered (i.e., by the arrival of a data object) rather than a program counter or clock driving movement of the data."

\_

<sup>&</sup>lt;sup>10</sup> Dr. Homayoun does not provide an opinion as to the proper interpretation of "systolic," but testifies that "[a] person or ordinary skill in the art would *not* consider the terms systolic, data driven, and seamless to have distinct meanings." Ex. 2111 ¶ 177 (emphasis added). We understand this to be a typographical error, given the preceding heading stating the opposite and Patent Owner's arguments in its Response. *See id.*; PO Resp. 34. We agree that "systolic" and "pass computed data seamlessly between said computational loops" in claim 1 have different meanings. Although both of our interpretations use the word "directly," we interpret the terms to mean different things. *See infra* Sections II.C.1, II.C.3. Nevertheless, the terms plainly are related, as claim 1 recites that the "systolic" implementation of the calculation is what "enables" the first and second computational loops to "pass computed data seamlessly between said computational loops."

# 2. "Computational Loop"

Claim 1 recites "utilizing a first of said instantiated functional units to operate upon a subsequent data dimension of said calculation forming a *first computational loop*" and "substantially concurrently utilizing a second of said instantiated functional units to operate upon a previous data dimension of said calculation forming a *second computational loop*" (emphases added).

In the Decision on Institution, we preliminarily interpreted "computational loop" in claim 1 to mean "a set of computations that is executed repeatedly, either a fixed number of times or until some condition is true or false." Dec. on Inst. 21–23. Petitioner agrees with that interpretation. Reply 35. Patent Owner states that it "does not disagree with" the preliminary interpretation, but "proposes a small clarification to reflect the plain and ordinary meaning of a loop within the field of high-performance computing and in particular in the context of the '324 Patent." PO Resp. 70. Specifically, Patent Owner proposes the following interpretation: "a set of computations that is executed repeatedly *per datum*, either a fixed number of times or until some condition is true or false." *Id.* at 69–70 (emphasis added).

Patent Owner in its Response cites three technical dictionary definitions of "loop," upon which we had based the preliminary interpretation as reflective of the plain meaning of the term. *See id.* at 70–71; Dec. on Inst. 21–23. None of those definitions, however, requires that a set of instructions or computations be executed repeatedly "per datum." *See* Ex. 2024, 4 ("[a] sequence of instructions that is repeated

<sup>&</sup>lt;sup>11</sup> Patent Owner's proposed interpretation in its Preliminary Response— "a sequence of computations that is repeated until a prescribed condition is satisfied"—did not include a "per datum" requirement. Paper 15, 21–22.

until a prescribed condition, such as agreement with a data element or completion of a count, is satisfied"); Ex. 2025, 5 ("a series of instructions being carried out repeatedly until a terminal condition prevails" or "[a] sequence of computer instructions that repeats itself until a predetermined count or other test is satisfied, or until the process is interrupted by operator intervention"); Ex. 2026, 8 ("[a] set of statements in a program executed repeatedly, either a fixed number of times or until some condition is true or false"); see also Ex. 2038, 3 (defining "computation" as "an act, process, or method of computing"). Indeed, Patent Owner cites the definitions in asserting that "[a] 'computational loop' is an iterative sequence of computations that repeats until a prescribed condition is satisfied" (without mentioning any "per datum" requirement). PO Resp. 80.

The Specification of the '324 patent is consistent with the technical dictionary definitions, and does not require that the set of computations executed repeatedly as a "loop" be on a particular piece of data. *See*Ex. 1001, col. 7, ll. 3–5 (explaining that computational process 610 "loops over the depth slices" and "loops over the shots" of a seismic imaging application), Fig. 7A (depicting three loops each performing computations a particular number of times as "k = 1, nz"; "j = 1, ny"; and "i = 1, nx"),

Fig. 8B (depicting two loops as "i = 1, l" and "k = 1, m"). Patent Owner does not cite—and we do not find—any specific support in the Specification (including a reference purportedly incorporated by reference in the '324 patent (Ex. 2037, "Caliga")) for imposing a "per datum" requirement. *See* PO Resp. 71–72 (citing Ex. 1001, col. 4, ll. 59–63, col. 6, ll. 1–30, col. 6, l. 47–col. 7, l. 48, col. 8, ll. 27–45, Figs. 4A–4B, 6B–6G, 7A, 8A–8B; Ex. 2037, 4, 5, 7, 12, 13, 16–19). Indeed, the Specification and Caliga do not use the term "datum." Caliga, in fact, describes the opposite of what

Patent Owner proposes, namely a "loop" of a set of computations executed repeatedly using *different* data. *See* Ex. 1076 ¶¶ 5–8; Ex. 2037, 5 (describing a "[l]oop over filter coefficients" where index j is incremented and different values for "Data", " $R_j$ ," and " $R_{j+1}$ " are used at each iteration); Reply 36.<sup>12</sup>

Patent Owner further cites as support U.S. Patent No. 8,589,666 B2 (Ex. 2027, "the '666 patent"), which was originally assigned to the same original assignee as the '324 patent (SRC Computers, Inc.) but is unrelated to the '324 patent. PO Resp. 72–73. The cited portions of the '666 patent generally describe a "loop body" with "new data" (plural) "fed in on every clock tick," and do not describe a "loop" as requiring a set of computations to be executed repeatedly "per datum" (singular). *See* Ex. 2027, col. 2, l. 64–col. 3, l. 23, col. 6, ll. 6–28. Dr. Homayoun also testifies that "[a] computational loop evaluates each piece of data multiple times, 'a fixed number of times or until some condition is true or false," but does not explain the basis for that interpretation, in the Specification of the '324 patent or otherwise. Ex. 2111 ¶ 207.

Finally, in its Sur-Reply and at the oral hearing, Patent Owner relied on Figure 4B of the '324 patent as support for its proposed interpretation, arguing that the figure "unambiguously describes . . . two loops A and B operating a number of times (looping) on *each* dimension of data" and that

\_

<sup>&</sup>lt;sup>12</sup> We do not agree with Patent Owner that Petitioner's Reply and Dr. Stone's reply testimony are improper, as they respond directly to Patent Owner's arguments in the Response regarding claim interpretation, where Patent Owner argued a "per datum" requirement for the first time. *See* Sur-Reply 8−9; Reply 36; Ex. 1076 ¶¶ 5−8; 37 C.F.R. § 42.23(b) ("A reply may only respond to arguments raised in the corresponding . . . patent owner response.").

our preliminary interpretation "would exclude from the claims the '324 Patent's embodiments and figures." *See* Sur-Reply 15–17; Tr. 52:20–58:21, 82:8–84:2. Patent Owner also stated during the oral hearing that "per datum" in its proposed interpretation could be replaced with "per dimension," as Patent Owner did not intend there to be a "difference" between the terms. Tr. 53:10–11, 55:3–10, 82:8–17.

We disagree for two reasons. First, claim 1 already recites two functional units operating on two data dimensions forming two computational loops. A first functional unit "operate[s] upon a subsequent data *dimension* of said calculation forming a first computational loop" and a second functional unit concurrently "operate[s] upon a previous data *dimension* of said calculation forming a second computational loop" (emphases added). Dependent claims 2–5 specify different options for what those dimensions may comprise, namely "multiple vectors," "multiple planes," "multiple time steps," or "multiple grid points" in the calculation. To the extent Patent Owner's proposed interpretation would require that a functional unit operate on a particular data "dimension" of the calculation forming a computational loop, that is already encompassed in the claim language.

Second, the Specification indicates that a data "dimension" is not the same thing as an individual "datum."

Figure 4B of the '324 patent is reproduced below.

Fig. 4B

Figure 4B depicts "multi-dimensional process 410 . . . effectuated such that multiple dimensions of data are processed by both Loops A (first loop 412) and B (second loop 414) such that the computing system logic is operative on every clock cycle." Ex. 1001, col. 6, ll. 13–20. An application

will "pass" a subsequent dimension of a given problem through the first loop 412 of logic concurrently with the previous dimension of data being processed through the second loop 414. In practice, a "dimension" of data can be: multiple vectors of a problem, multiple planes of a problem, multiple time steps in a problem and so forth.

*Id.* at col. 6, ll. 24–30 (emphasis added). The Specification uses the phrasing "dimension" "of data" or "dimension" "of a given problem," not "datum" individually, and provides examples of possible dimensions that mirror the

language of dependent claims 2–5. It does not describe loop calculations applied to the same individual "datum" repeatedly.<sup>13</sup>

Having reviewed all of the cited evidence, we do not find sufficient support for limiting the term "computational loop" to require that computations be executed repeatedly "per datum." Applying the broadest reasonable interpretation of the claims in light of the Specification, we interpret "computational loop" to mean "a set of computations that is executed repeatedly, either a fixed number of times or until some condition is true or false."

3. "Pass Computed Data Seamlessly Between Said Computational Loops"

Claim 1 recites that "said systolic implementation of said calculation enables said first computational loop and said second computational loop execute<sup>14</sup> concurrently and pass computed data seamlessly between said computational loops."

Petitioner argues that "pass computed data seamlessly between said computational loops" in claim 1 means "communicate computed data

<sup>&</sup>lt;sup>13</sup> The parties do not refer to anything in the prosecution history as supporting their proposed interpretations of "computational loop." During prosecution, the applicants initially proposed (during the examiner interview discussed above in connection with the term "systolic") amending claim 1 to recite that "said first of said instantiated functional units and said second of said instantiated functional units are within a nested loop of said calculation." Ex. 1002, 208–209. The applicants then instead amended the claim to recite, rather than a "nested loop," first and second "computational loops" executing concurrently with computed data seamlessly passed between them. *Id.* at 214–215.

<sup>&</sup>lt;sup>14</sup> We read the claim language to mean that the systolic implementation enables the loops "to" execute concurrently and pass computed data seamlessly between the computational loops.

directly between functional units that are calculating computational loops." Pet. 19; Reply 20. Based on the record at the time, we preliminarily agreed with Petitioner's proposed interpretation in the Decision on Institution. Dec. on Inst. 23–26. Patent Owner argues that the phrase instead should be interpreted to mean "communicating the computed data over the reconfigurable routing resources." PO Resp. 34–35.

According to the plain language of the claim, which recites "pass[ing] computed data seamlessly between said computational loops," "seamlessly" refers to how computed data is passed *between* the first and second computational loops (performed by the first and second functional units of the reconfigurable processor)—not, for example, how computed data is passed from either of the computational loops to any other component unrelated to the functional units, or vice versa.

The only other time "seamlessly" appears in the '324 patent is in independent claims 25 and 51, which mirror the language of claim 1, reciting that computed data is passed "seamlessly" between systolic walls or columns of a calculation. The written description does not use the terms "seam" or "seamlessly." Figure 2, though, shows functional units 204 interconnected without any intervening structures between them, which is consistent with Petitioner's proposed interpretation. *See* Ex. 1001, col. 5, ll. 41–47. Figures 7A–7B and 8A–8B similarly show direct communication of data from one computational loop to another. *See id.* at col. 7, l. 42–col. 8, l. 6 (loops 702, 704, and 706), col. 8, ll. 27–55 (loops 812 and 814). Although the description of the figures does not use the terms "seam" or "seamlessly," a person of ordinary skill in the art would have understood the claim language in light of that description, given that it describes and

IPR2018-01601 Patent 7,225,324 B2

shows the interaction between multiple "loops," as recited in claim 1. *See id.*

The prosecution history of the '324 patent also supports Petitioner's proposed interpretation. The applicants added the "seamlessly" language to claim 1 in the Office Action response discussed above in connection with the term "systolic." Ex. 1002, 214–215. In response to the § 112, first paragraph, written description rejection, the applicants indicated that data from one functional unit performing a computational loop is passed directly to another functional unit:

Data flows across the array between functional units, usually with different data flowing in different directions. . . . [I]n the Applicant's invention Systolic implementation will connect computational loops such that data from one compute loop will be passed as input data to a concurrently executing compute loop. In the Applicant's invention data computed by computation units or groups of functional units flows seamlessly and concurrently with data being computed by other groups of functional units. Thus, the process claimed by the Applicant therefore significantly increases the computing processes taking place in a reconfigurable processor.

Ex. 1002, 226. Although the language above primarily relates to the term "[s]ystolic," we also find it significant for purposes of interpreting the "seamlessly" phrase because it refers to the limitation expressly in describing "Applicant's invention." *See id.*; Ex. 1003 ¶ 98; *Shire Dev., LLC v. Watson Pharms., Inc.*, 787 F.3d 1359, 1366 (Fed. Cir. 2015) (holding that even where "prosecution history statements do not rise to the level of unmistakable disavowal, they do inform the claim construction").

Finally, Petitioner's proposed interpretation is consistent with the testimony of Mr. Huppenthal, one of the named inventors of the '324 patent, who describes "interpret[ing] standard high level language program

constructs, such as the fact that the output variable from one loop is the input to another, and then implement[ing] this as a *storage free, seamless* connection between the two loops implemented on the FPGA," and states:

By seamlessly I mean that the results of one loop streamed from that loop's output to the input of the next loop without being placed in a circuit element that required explicit address based on read or write operations such as a data register or memory or through a switch that requires additional non-data content for routing purposes.

Ex.  $2100 \, \P \, 78$  (emphases added).

Based on our review of the full record after trial, Patent Owner's arguments regarding the "seamlessly" language in claim 1 are not persuasive. See PO Resp. 34-42; Sur-Reply 20-21. First, Patent Owner relies on portions of the Specification describing interaction of cells "at the boundary," "the problem of passing data over numerous boundaries (or seams) between processing elements in typical multi-processor systems," and the '324 patent's solution to that problem of "staying on a single FPGA chip, effectively eliminating the associated boundaries or seams from chip-to-chip communication." PO Resp. 35–36, 39 (citing Ex. 1001, col. 2, 11. 25–48) (emphasis omitted); see Ex. 2111 ¶¶ 160–162. The cited portions of the Specification do not use the terms "seam" or "seamlessly" and, unlike the portions cited by Petitioner describing Figures 7A–7B and 8A–8B, do not describe interaction between "loops" in the disclosed method. We find them less relevant than the portions discussed above, particularly given that the claim language at issue recites passing computed data seamlessly "between" the computational loops (performed by the functional units of the reconfigurable processor).

Second, Patent Owner relies on certain statements made by the applicants during prosecution of the '324 patent. PO Resp. 36–39; *see* Ex. 2111 ¶¶ 163–166. Three of those statements mirror the Specification language cited by Patent Owner and, importantly, predate the addition of the "seamlessly" language to claim 1 (and likewise do not use the terms "seam" or "seamlessly"). *See* Ex. 1002, 117–118, 148–150, 174–175. In addition, Patent Owner cites the following statement by the applicants in the Office Action response discussed above:

The instantiation of the at least one reconfigurable processor with at least two functional units enables each functional unit to communicate with each other. Certainly communication between other reconfigurable processors within the system would require [a] communication protocol but communication between functional units within an individual reconfigurable processor is free of such a requirement. To alleviate any confusion, the reference to the term "protocol" has been replaced with an "interconnection" between functional units that is established by reconfigurable routing resources inside each chip.

*Id.* at 224–25; *see* PO Resp. 37–39. The cited language pertains to the "instantiating" step recited earlier in the claim, which also was amended in the response, including replacing "communications . . . independent of external and internal communication protocols" with "interconnects . . . based on reconfigurable routing resources." *See* Ex. 1002, 214, 224–25. By contrast, the applicants added the "seamlessly" limitation to specify the interaction between the computational loops (i.e., that computed data is passed "seamlessly" between them).

Third, Patent Owner disputes the "directly" aspect of Petitioner's proposed interpretation because "it would exclude standard FPGAs . . . since standard FPGAs contain reconfigurable routing resources (comprising buffers and switches) between the configurable logic blocks," and thus

would "exclude the very embodiments of the '324 Patent." PO Resp. 40–41, 47–48 (citing Ex. 1035, 31; Ex. 2078, 19–29, 32–34, 37–41, 46–51, 59–65). We agree with Petitioner that "[j]ust because a standard FPGA may include memories does not mean that when functional units are instantiated within such an FPGA that the memories are necessarily placed *between* functional units." *See* Reply 25. Claim 1 recites two functional units being instantiated and concurrently performing two computational loops, with computed data passed seamlessly between the computational loops. Petitioner's proposed interpretation of the "seamlessly" phrase correctly pertains to how computed data is passed *between* the computational loops when so instantiated, and is not inconsistent with the mere existence of memory on an FPGA.

Fourth, Patent Owner argues that the word "directly" makes

Petitioner's proposed interpretation unreasonable because it "introduce[s] ambiguity and confusion." PO Resp. 36, 40–41; see Ex. 2111 ¶¶ 169–176.

According to Patent Owner, Dr. Stone on cross-examination could not identify what "intervening" structures would prevent direct communication, and contradicted himself by stating that "an intervening memory would not be a direct connection" and later that "if a register . . . were between the two processing elements then the connection would still be direct, but if the intervening structure were a buffer then the connection would not be direct."

PO Resp. 41 (citing Ex. 2064, 86:13–91:24). Patent Owner argues that if Dr. Stone's view is adopted, "[t]he same circuit would be both direct and indirect, depending on where the boundaries of the 'processing element' are arbitrarily drawn with respect to intervening structures." Sur-Reply 20–21.

We disagree that the word "directly" in Petitioner's proposed interpretation is unclear or that Dr. Stone's testimony about it introduces ambiguity. Dr. Stone testified as follows:

- Q. Okay. And you mention the word "directly," it was passing data directly between processing elements. What does that phrase mean to you or what's the context? What are you trying to describe there?

- A. That the data goes from first to the second *without going* to something intervening. It directly go is connected immediately. Indirectly we you go through one or more intervening places to get there.

- Q. Okay. So would memory, if the data was going from one processing element to memory and then back to a processing element, is that something you would consider as an intervening thing?

- A. Well, that would not be a direct connection of the output of the cell to the next cell. It says, "Between processing elements you're directly connected." If you're saying you have a processing element outputting to memory and then coming back to another processing element, that would not be direct.

Ex. 2064, 85:14–86:12 (emphases added). When asked about a register in particular, Dr. Stone testified as follows:

- Q. Well, how about a a register? Would that be an intervening structure?

- A. I I'm puzzled because that that register would be within within the processing element in my mind.

- Q. Okay.

- A. If it's within the processing element as a register, yeah, I would put it there, then the output of that register, if it's connected directly to the input of the next processing element, would be direct.

*Id.* at 86:19–87:5 (emphases added); *see also id.* at 87:23–25 ("If the register is part of the processing element, then the connection would be direct.").

Data is not communicated "directly" between processing elements when it is communicated through an intervening structure *between* them. *See id.* at 85:14–91:24. Examples of such a structure are memory and

another processing element, but logically others are possible as well depending on how they are situated with respect to the processing elements. *See id.* at 86:13–18. When a register is *within* a processing element, however, data can still be communicated "directly" (provided there is a direct connection between the processing elements), as Dr. Stone explained. *See id.* at 85:14–91:24. We do not see any ambiguity in making this distinction. The boundaries of a processing element are not arbitrary as Patent Owner contends, but rather, in the context of a particular written document, would depend on how the reference describes the processing element and the communication of data to and from the processing element. *See, e.g.*, Ex. 1001, Fig. 2 (depicting functional units 204 of adaptive processor chip 202). Logically, also, in an arrangement with multiple processing elements, there must be some division between the processing elements, otherwise there would not be multiple elements. *See* Tr. 14:1–5.

Applying the broadest reasonable interpretation of the claims in light of the Specification, we interpret "pass computed data seamlessly between said computational loops" to mean "communicate computed data directly between functional units that are calculating computational loops."

### 4. "Establishing a Stream Communication Connection Between Functional Units"

Claim 15 depends from claim 1 and recites that "instantiating includes establishing a stream communication connection between functional units" (the "stream communication" limitation). Petitioner argues that "stream communication" should be interpreted to mean "communication of a data sequence." Pet. 19–21. Patent Owner argues that "stream communication" means "a data path that acts like a queue connecting via the reconfigurable

routing resources a producer and a consumer of data that operate concurrently." PO Resp. 50–69. We did not preliminarily interpret "stream communication" in the Decision on Institution.

We begin with the language of the claim. Claim 15 recites that "instantiating" includes establishing a stream communication connection "between functional units." "[I]nstantiating" in claim 15 refers to the "instantiating" step of parent claim 1 (emphasis added):

instantiating at least two of said functional units at the at least one reconfigurable processor to perform said calculation wherein only functional units needed to solve the calculation are instantiated and wherein each instantiated functional unit at the at least one reconfigurable processor interconnects with each other instantiated functional unit at the at least one reconfigurable processor based on reconfigurable routing resources within the at least one reconfigurable processor as established at instantiation . . . .

Thus, according to the plain language of the claim, what is being "instantiat[ed]" is the at least two "functional units." The "reconfigurable routing resources," based on which the instantiated functional units are "interconnect[ed]," are established "at" the instantiation.

Turning to the language of claim 15, regardless of whether "stream communication" is used as an adjective (as Petitioner contends) or a noun (as Patent Owner contends), the term appears immediately before and modifies the phrase "connection between functional units." *See* Reply 30–31; Sur-Reply 10 & n.2. The claim, therefore, requires establishing a connection of a particular type, namely a "stream communication" type of connection. Nothing further in the language of the claim limits or sheds light on what that type of connection entails.

Nor does the Specification. The only other time "stream communication" appears in the '324 patent is in claim 40, which mirrors the language of claim 15. The written description never uses the term. <sup>15</sup> It also does not differentiate between different types of connections between functional units.

Both parties, however, refer to patents that the '324 patent purports to incorporate by reference. *See* Pet. 20–21; PO Resp. 62–66. The '324 patent states that it is "related to the subject matter of," and "incorporate[s] in [its] entirety by . . . reference," U.S. Patent No. 6,434,687 B1 (Ex. 1014, "the '687 patent"). Ex. 1001, col. 1, ll. 9–20. Petitioner points to the phrase "streams of operands" in the '687 patent as supporting its proposed interpretation. Pet. 20. The cited portion describes multi-adaptive (MAP) processor 112 with reconfigurable array 42 having one or more high performance FPGAs. Ex. 1014, col. 9, ll. 1–6. "After configuration, the user array 42 can perform whatever function it was programmed to do." *Id.* at col. 9, ll. 11–12. "In order to maximize its performance for vector processing, the array 42 should be able to access two streams of operands simultaneously" by using a chain port "connector allow[ing] the MAP element 112 to use data provided to it by a previous MAP element 112." *Id.* at col. 9, ll. 12–26.

<sup>&</sup>lt;sup>15</sup> Petitioner argues that its proposed interpretation is consistent with a portion of the Specification describing systolic wall of computation 712 in Figure 7C and stating that "communication of values between adjacent rows . . . in the virtual wall can occur without storing values to memory." Ex. 1001, col. 8, ll. 7–12; *see* Pet. 20–21; Ex. 1003 ¶ 117. The cited portion, however, never uses the term "stream communication."

<sup>&</sup>lt;sup>16</sup> Petitioner challenges the '687 patent in Case IPR2018-01594.

We find the cited portion to be of limited relevance. The '687 patent uses "streams of operands" rather than "stream communication" and does not describe the "streams of operands" other than the single sentence above. Also, given the length of the '687 patent disclosure, it is unclear exactly what aspects of the '687 patent are incorporated in the '324 patent or how they would apply in the context of the '324 patent invention. *See* Ex. 1001, col. 1, ll. 9–20 (merely stating that the '324 patent is "related to the subject matter of" the '687 patent). If anything, the cited portion of the '687 patent simply indicates that certain data (i.e., "operands") can be streamed from one MAP element to another.

Patent Owner similarly quotes other excerpts from the '687 patent describing the use of a chain port connection, input buffer 40, and output First-In-First-Out (FIFO) buffer 74 in support of its contention that "stream communication" requires a "data path" acting like a "queue." PO Resp. 63–66 (citing Ex. 1014, col. 7, ll. 43–57, col. 8, ll. 7–26, col. 9, ll. 2–67); see Ex. 1014, Figs. 6–7. We are not persuaded for the same reasons as Petitioner's citation. The cited portions merely describe an exemplary embodiment of the '687 patent that uses memory buffers. Other than the single use of "streams of operands," there is no connection between the '687 patent disclosure and anything pertaining to streaming. See Sur-Reply 12 (acknowledging that the '687 patent is "a different patent referring to a different invention pertaining to internet communications"). Certainly, the cited portions do not use or define what is meant by "establishing a stream communication connection between functional units" in the context of the data processing method recited in claim 15.

Patent Owner also relies on U.S. Patent No. 6,339,819 B1 (Ex. 2085, "the '819 patent"), of which the '687 patent is a continuation-in-part, as

incorporated by reference in the '324 patent. PO Resp. 62–64. The '324 patent describes "a representative systolic wavefront operation in the form of a reservoir simulation function" where